k8凯发(中国)天生赢家·一触即发

首页 > k8凯发(中国)天生赢家·一触即发

首页 > k8凯发(中国)天生赢家·一触即发

凯发在线平台芯和半导体:三款“王炸”EDA产品精准应对高速链路中的“痛点”|欧联

来源:凯发娱发K8官网 发布时间:2025-02-14

作为芯片设计的工具ღ★✿ღ,EDA贯穿了集成电路产业链的每个环节ღ★✿ღ,赋能集成电路设计与制造的创新升级ღ★✿ღ,被誉为“芯片设计之母”ღ★✿ღ。当前ღ★✿ღ,在人工智能ღ★✿ღ、5Gღ★✿ღ、物联网ღ★✿ღ、智能网联汽车等新兴市场快速发展的推动下ღ★✿ღ,高速高频系统中的信号ღ★✿ღ、电源ღ★✿ღ、电磁兼容等新型问题层出不穷ღ★✿ღ,为EDA设计带来了全新的挑战ღ★✿ღ。

作为国内EDA行业的领军企业凯发在线平台ღ★✿ღ,芯和半导体科技(上海)股份有限公司(Xpeedicღ★✿ღ,简称“芯和半导体”)通过自研EDA产品和解决方案ღ★✿ღ,提供覆盖ICღ★✿ღ、封装到系统的全产业链高速高频仿真EDA解决方案ღ★✿ღ,可满足高速链路中不同应用场景的设计要求ღ★✿ღ。

4月18日ღ★✿ღ,集微网举办第63期“集微公开课”活动ღ★✿ღ,特邀芯和半导体技术专家ღ★✿ღ,以“从DesignCon技术趋势看国内高速系统EDA”为主题欧联首个六冠王诞生ღ★✿ღ,为大家分享系统设计领域中所使用的领先EDA工具之最新技术规划蓝图与未来发展趋势ღ★✿ღ,以及讲解芯和半导体自主研发的Notusღ★✿ღ、Hermes 3Dღ★✿ღ、ChannelExpert三款EDA工具在系统设计应用中的产品特性ღ★✿ღ、优势特点等ღ★✿ღ。

今年2月ღ★✿ღ,DesignCon2023技术大会在美国加州落下帷幕ღ★✿ღ。会上ღ★✿ღ,芯和半导体正式发布针对封装及板级的信号完整性欧联首个六冠王诞生ღ★✿ღ、电源完整分析和热分析的全新EDA平台Notusღ★✿ღ;同时凯发在线平台ღ★✿ღ,以第一视角获得DesignCon2023大会中关于信号完整性ღ★✿ღ、电源完整性和射频设计等应用领域的前沿技术趋势ღ★✿ღ。

芯和高速技术专家Brian介绍ღ★✿ღ,本次DesignCon2023大会聚焦高速数字设计ღ★✿ღ、光通信ღ★✿ღ、5G人工智能ღ★✿ღ、先进封装等热门产业凯发在线平台ღ★✿ღ,提及224 Gbps以太网ღ★✿ღ、PCIe 6.0ღ★✿ღ、USB-4 v2以及芯片封装工艺等下一代推动电子设计发展的技术趋势ღ★✿ღ。会上ღ★✿ღ,“高速串行信号以太网”ღ★✿ღ、“高速串行信号PCIe”ღ★✿ღ、“高速并行信号DDR”等话题引起热议ღ★✿ღ,并探讨关于PCB材料SI&testღ★✿ღ、过孔优化ღ★✿ღ、直流阻隔电容器ღ★✿ღ、线缆和连接器ღ★✿ღ、电源完整性等方面的新技术ღ★✿ღ。

“随着下一代以太网ღ★✿ღ、DDRღ★✿ღ、PCIeღ★✿ღ、先进封装等技术的革新凯发在线平台ღ★✿ღ,机遇与挑战并存ღ★✿ღ。”Brian表示ღ★✿ღ,为应对全新挑战ღ★✿ღ,紧抓发展机遇ღ★✿ღ,芯和也规划了高速系统EDA工具未来发展“蓝图”ღ★✿ღ。

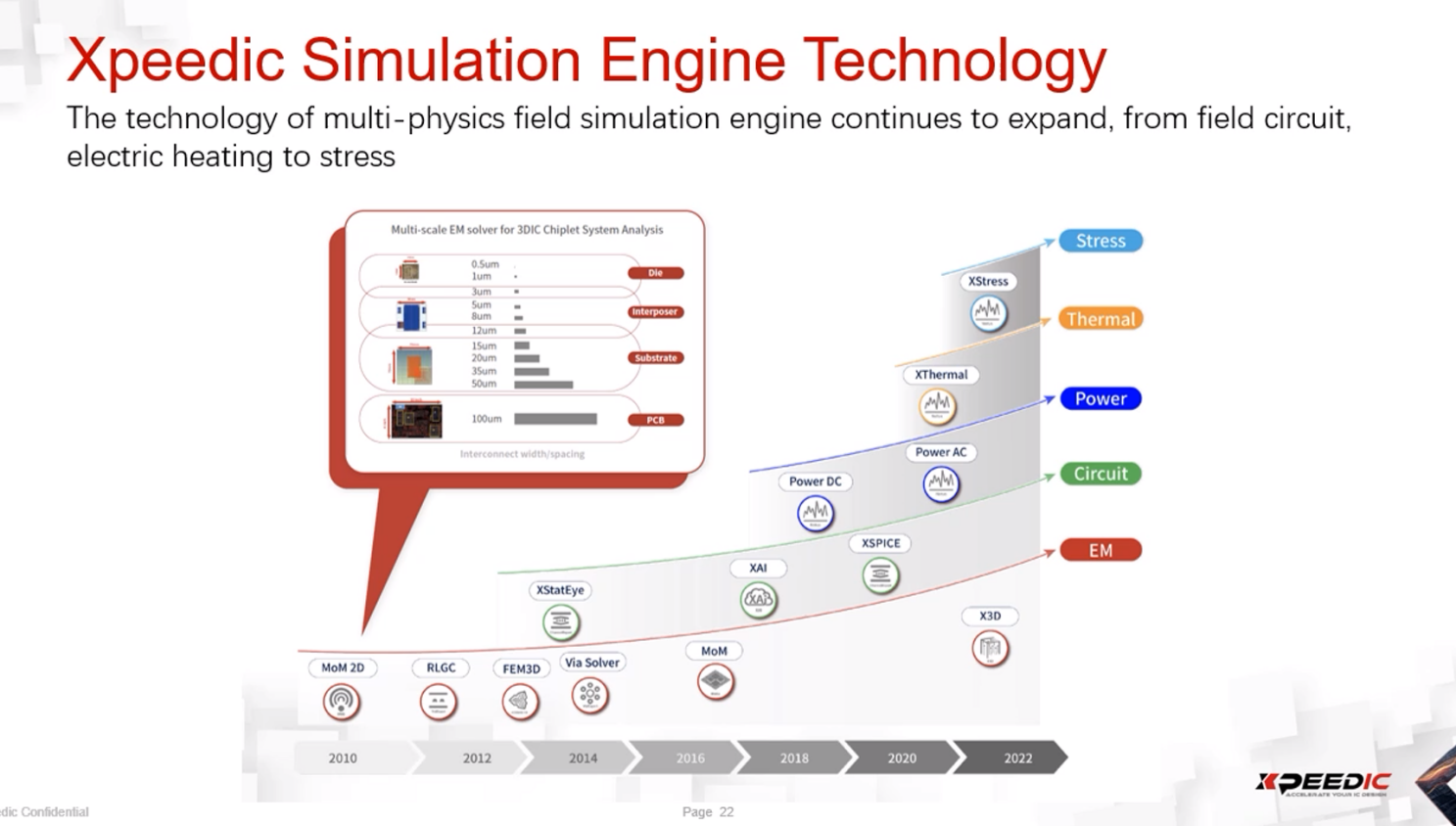

“芯和的核心竞争力在于其先进而丰富的求解器技术ღ★✿ღ:在电磁仿真方面ღ★✿ღ,芯和的求解技术实现从矩量法到有限元ღ★✿ღ,并衍生了Via和RLGC等电磁引擎ღ★✿ღ;准静态有限元求解器去年已开始研发凯发k8·[中国]官方网站ღ★✿ღ,ღ★✿ღ,预计今年下半年推出ღ★✿ღ。在电路方面ღ★✿ღ,芯和完善了统计ღ★✿ღ、损态和时域仿真技术ღ★✿ღ,应用于电路仿真的spice求解器预计今年将普及到ChannelExpert和XDS工具上ღ★✿ღ。在电源仿真方面ღ★✿ღ,芯和开发了DCღ★✿ღ、AC求解器ღ★✿ღ。此外ღ★✿ღ,芯和也在布局热应力方向ღ★✿ღ,同时完成对先进封装和高速数字解决方案的重要升级ღ★✿ღ。”Brian透露ღ★✿ღ,随着今年即将发布的X3D和Xspice求解器引擎的导入ღ★✿ღ,芯和将实现从芯片ღ★✿ღ、封装到系统的设计与仿真全覆盖凯发国际k8官网ღ★✿ღ,ღ★✿ღ,可高效联动Fabless和Foundryღ★✿ღ。

随着高电流密度ღ★✿ღ、低工作电压的高速数字系统发展趋势ღ★✿ღ,对于负载芯片的电源纹波规格要求更加严格ღ★✿ღ。而信号快速切换引起的平面电压波动和高功率器件工作引起的温升效应皆会导致芯片供电不稳定和信号噪声过大ღ★✿ღ。因此在PCB系统设计阶段进行电源完整性分析至关重要ღ★✿ღ。

“电源完整性设计主要是为芯片提供干净稳定的电压ღ★✿ღ,把负载芯片电源波动(DC&AC)控制在芯片SPEC内凯发国际k8官网登录手机天生赢家·一触即发ღ★✿ღ。ღ★✿ღ!ღ★✿ღ,同时避免电源噪音干扰信号ღ★✿ღ。”芯和技术支持工程师Carrie表示ღ★✿ღ。

Carrie指出ღ★✿ღ,当前的系统向着低压大电流ღ★✿ღ、高密小型化ღ★✿ღ、高速高带宽的趋势演进ღ★✿ღ。低压大电流带来的电源通道压降增大ღ★✿ღ、芯片可容忍压降变小ღ★✿ღ,使得对目标阻抗设计要求变得更加严苛ღ★✿ღ;高密小型化引起的布线通道有限ღ★✿ღ、去耦电容数量受空间限制ღ★✿ღ、发热问题等ღ★✿ღ;高速高带宽引起的高速信号速率提升ღ★✿ღ、对电源噪声更加敏感等问题ღ★✿ღ,都对系统的电源完整性提出了更高的要求ღ★✿ღ。

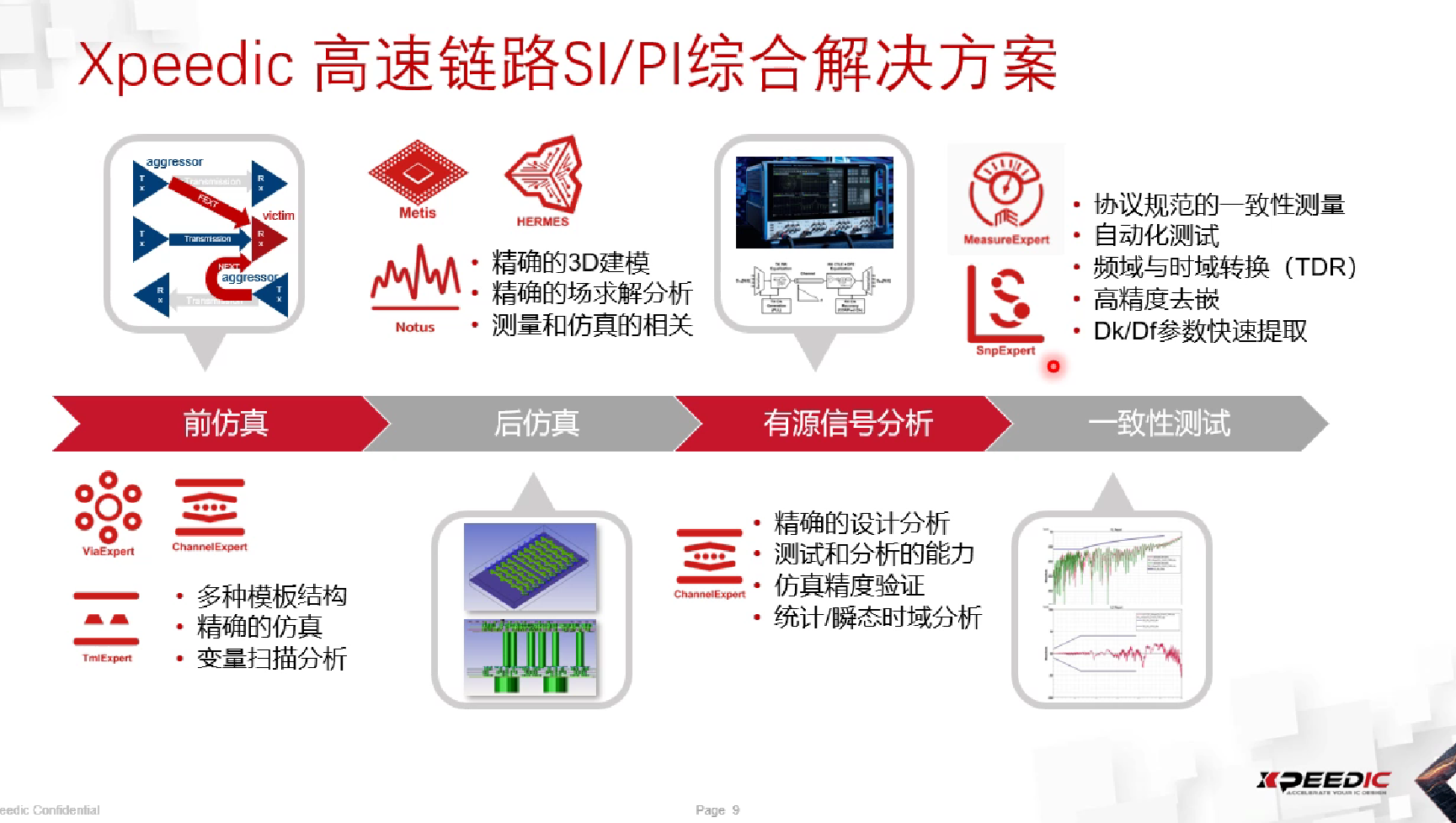

对此ღ★✿ღ,芯和可提供包含前仿真ღ★✿ღ、后仿真ღ★✿ღ、有源信号分析ღ★✿ღ、一致性测试等在内的高速链路SI/PI综合解决方案ღ★✿ღ,并推出SI/PI仿真平台——Notusღ★✿ღ。

Carrie介绍道ღ★✿ღ,Notus主要包括PI分析和SI分析ღ★✿ღ,并支持封装级ღ★✿ღ、板级和多板联合的电源完整性分析ღ★✿ღ。PI分析主要是为设计者提供DC直流压降ღ★✿ღ、AC频域阻抗ღ★✿ღ、ET电热协同的仿真分析流程ღ★✿ღ;SI分析主要提供S参数提取和低速拓扑仿真两个分析流程ღ★✿ღ。Notus基于芯和强大的电磁场和多物理仿真引擎技术ღ★✿ღ,功能强大ღ★✿ღ、易于上手ღ★✿ღ,可帮助设计者获得去耦电容组合最佳化方案ღ★✿ღ,达到物料成本k8凯发(中国)官方网站ღ★✿ღ,ღ★✿ღ、产品性能和生产良率之间的最佳设计平衡点欧联首个六冠王诞生ღ★✿ღ。

在高速传输数字系统设计中ღ★✿ღ,芯片封装ღ★✿ღ、连接器与PCB联合结构链路上的封装Wire bondღ★✿ღ、焊球及焊盘ღ★✿ღ、Via stub等因素ღ★✿ღ,皆会导致传输信号衰减ღ★✿ღ、阻抗突变和信号串扰等问题ღ★✿ღ,进而严重影响高速传输数字系统中信号与电源的完整性ღ★✿ღ。

芯和技术支持工程师Jay指出ღ★✿ღ,当前ღ★✿ღ,是否能支持主流设计文件Cadenceღ★✿ღ、Mentor半导体ღ★✿ღ,ღ★✿ღ、Autocad等的导入凯发在线平台ღ★✿ღ,支持任意三维结构ღ★✿ღ:如连接器ღ★✿ღ、AC电容模型ღ★✿ღ、PCB的任意3D结构建模ღ★✿ღ,支持封装ღ★✿ღ、封装与PCB联合结构下电源凯发在线平台ღ★✿ღ、高速信号的S参数提取ღ★✿ღ,支持高精度高性能求解等都是后仿真工具所面临的挑战ღ★✿ღ。设计者需要精准萃取联合结构链路参数ღ★✿ღ,进行仿真优化ღ★✿ღ,以获取最佳化产品性能ღ★✿ღ。

对此ღ★✿ღ,芯和推出具有自主知识产权ღ★✿ღ,内嵌业内领先的自适应网格切分技术与三维全波电磁场仿线D Solver(FEM3D)ღ★✿ღ。

Jay表示ღ★✿ღ,FEM3D采用自适应网络剖分技术结合有限元(FEM)求解技术以及分布式集群模拟加速技术(XHPC)凯发在线平台ღ★✿ღ,可以满足任意三维结构的电磁场求解ღ★✿ღ,求解精度可覆盖到太赫兹(THz)频率ღ★✿ღ,能大幅度提高求解效率ღ★✿ღ;支持参数化建模ღ★✿ღ,实现模型的扫描优化分析ღ★✿ღ;可用于PCBღ★✿ღ、封装ღ★✿ღ、连接器等任意3D模型的联合建模的EM仿真求解ღ★✿ღ,精确提取高速信号ღ★✿ღ、电源模型的S参数K8天生赢家一触发ღ★✿ღ,ღ★✿ღ,并实现电磁场分布分析ღ★✿ღ,帮助设计者解决信号与电源完整性分析中的痛点ღ★✿ღ。

芯和技术支持工程师Lily表示ღ★✿ღ,随着人工智能ღ★✿ღ、5Gღ★✿ღ、HPC等场景的应用ღ★✿ღ,促使芯片设计走向异构集成及系统化ღ★✿ღ,使得PCB高速传输信号完整性面临多重挑战ღ★✿ღ,包括先进制程引入的损耗欧联首个六冠王诞生ღ★✿ღ、串扰ღ★✿ღ、电源噪声等问题使得链路性能变差ღ★✿ღ;低压大电流ღ★✿ღ、复杂的封装形式增大了设计难度ღ★✿ღ;速率越来越高ღ★✿ღ,产品越来越复杂ღ★✿ღ,过去的经验设计可能不再适用等ღ★✿ღ。

Lily指出ღ★✿ღ,工程师通常可以采用Bit-By-Bit(逐比特分析)ღ★✿ღ、Statistical(统计分析)和PDA(峰值失真分析)等眼图分析方法凯发在线平台ღ★✿ღ,去判断高速链路传输的信号质量ღ★✿ღ。其中ღ★✿ღ,PDA可快速获取最差的眼图轮廓线ღ★✿ღ,减少仿真运算量ღ★✿ღ。

针对包含SerDes/DDR在内的高速链路系统ღ★✿ღ,芯和推出用于高速数字信号链路仿真与分析软件ChannelExpertღ★✿ღ。

Lily介绍道ღ★✿ღ,ChannelExpert可实现DDR时域仿真分析ღ★✿ღ,包括基于DDR BUS的时域仿线-BIT的时域仿真分析ღ★✿ღ、DDR总线SSN仿真分析等ღ★✿ღ;ChannelExpert还可实现Serdes时域分析ღ★✿ღ,支持基于模板快速建立信道ღ★✿ღ、基于IBIS-AMI模型仿真分析ღ★✿ღ、基于理想TX/RX的SerDes通道分析等欧联首个六冠王诞生ღ★✿ღ。

Lily表示ღ★✿ღ,ChannelExpert可通过瞬态ღ★✿ღ、统计进行眼图分析欧联首个六冠王诞生ღ★✿ღ,评估链路信号质量ღ★✿ღ,PDA算法提前预判worst case的码型和内眼图ღ★✿ღ,减少仿真时间ღ★✿ღ;同时ღ★✿ღ,内置业内先进的时域仿真引擎和频域级联技术ღ★✿ღ,能更便捷ღ★✿ღ、更准确地建模和进行通道仿真ღ★✿ღ,帮助设计者快速检查关键路径信号完整性指标ღ★✿ღ,规避信号质量风险ღ★✿ღ,缩短产品周期ღ★✿ღ。